# NEHRU COLLEGE OF ENGINEERING AND RESEARCH CENTRE (NAAC Accredited)

(Approved by AICTE, Affiliated to APJ Abdul Kalam Technological University, Kerala)

# DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

# **COURSE MATERIALS**

EC 206: COMPUTER ORGANISATION

#### VISION OF THE INSTITUTION

To mould true citizens who are millennium leaders and catalysts of change through excellence in education.

# MISSION OF THE INSTITUTION

**NCERC** is committed to transform itself into a center of excellence in Learning and Research in Engineering and Frontier Technology and to impart quality education to mould technically competent citizens with moral integrity, social commitment and ethical values.

We intend to facilitate our students to assimilate the latest technological know-how and to imbibe discipline, culture and spiritually, and to mould them in to technological giants, dedicated research scientists and intellectual leaders of the country who can spread the beams of light and happiness among the poor and the underprivileged.

#### ABOUT DEPARTMENT

♦ Established in: 2002

♦ Course offered: B.Tech in Electronics and Communication Engineering

# M.Tech in VLSI

- ♦ Approved by AICTE New Delhi and Accredited by NAAC

- ♦ Affiliated to the A P J Abdul Kalam Technological University.

# **DEPARTMENT VISION**

Provide well versed, communicative Electronics Engineers with skills in Communication systems with corporate and social relevance towards sustainable developments through quality education.

# **DEPARTMENT MISSION**

- 1) Imparting Quality education by providing excellent teaching, learning environment.

- 2) Transforming and adopting students in this knowledgeable era, where the electronic gadgets (things) are getting obsolete in short span.

- 3) To initiate multi-disciplinary activities to students at earliest and apply in their respective fields of interest later.

- 4) Promoting leading edge Research & Development through collaboration with academia & industry.

#### PROGRAMME EDUCATIONAL OBJECTIVES

- PEO1. To prepare students to excel in postgraduate programmes or to succeed in industry / technical profession through global, rigorous education and prepare the students to practice and innovate recent fields in the specified program/ industry environment.

- PEO2. To provide students with a solid foundation in mathematical, Scientific and engineering fundamentals required to solve engineering problems and to have strong practical knowledge required to design and test the system.

- PEO3. To train students with good scientific and engineering breadth so as to comprehend, analyze, design, and create novel products and solutions for the real life problems.

- PEO4. To provide student with an academic environment aware of excellence, effective communication skills, leadership, multidisciplinary approach, written ethical codes and the life-long learning needed for a successful professional career.

# **PROGRAM OUTCOMES (POS)**

# **Engineering Graduates will be able to:**

- 1. **Engineering knowledge**: Apply the knowledge of mathematics, science, engineering fundamentals, and an engineering specialization to the solution of complex engineering problems.

- 2. **Problem analysis**: Identify, formulate, review research literature, and analyze complex engineering problems reaching substantiated conclusions using first principles of mathematics, natural sciences, and engineering sciences.

- 3. **Design/development of solutions**: Design solutions for complex engineering problems and design system components or processes that meet the specified needs with appropriate consideration for the public health and safety, and the cultural, societal, and environmental considerations.

- 4. **Conduct investigations of complex problems**: Use research-based knowledge and research methods including design of experiments, analysis and interpretation of data, and synthesis of the information to provide valid conclusions.

- 5. **Modern tool usage**: Create, select, and apply appropriate techniques, resources, and modern engineering and IT tools including prediction and modeling to complex engineering activities with an understanding of the limitations.

- 6. **The engineer and society**: Apply reasoning informed by the contextual knowledge to assess societal, health, safety, legal and cultural issues and the consequent responsibilities relevant to the professional engineering practice.

- 7. **Environment and sustainability**: Understand the impact of the professional engineering solutions in societal and environmental contexts, and demonstrate the knowledge of, and need for sustainable development.

- 8. **Ethics**: Apply ethical principles and commit to professional ethics and responsibilities and norms of the engineering practice.

- 9. **Individual and team work**: Function effectively as an individual, and as a member or leader in diverse teams, and in multidisciplinary settings.

- 10. **Communication**: Communicate effectively on complex engineering activities with the engineering community and with society at large, such as, being able to comprehend and write effective reports and design documentation, make effective presentations, and give and receive clear instructions.

- 11. **Project management and finance**: Demonstrate knowledge and understanding of the engineering and management principles and apply these to one's own work, as a member and leader in a team, to manage projects and in multidisciplinary environments.

- 12. **Life-long learning**: Recognize the need for, and have the preparation and ability to engage in independent and life-long learning in the broadest context of technological change.

# PROGRAM SPECIFIC OUTCOMES (PSO)

**PSO1**: Facility to apply the concepts of Electronics, Communications, Signal processing, VLSI, Control systems etc., in the design and implementation of engineering systems.

**PSO2**: Facility to solve complex Electronics and communication Engineering problems, using latest hardware and software tools, either independently or in team.optimization.

# COURSE OUTCOMES EC 206

|        | SUBJECT CODE: EC 206                                                                                         |

|--------|--------------------------------------------------------------------------------------------------------------|

|        | COURSE OUTCOMES                                                                                              |

| C206.1 | Ability to illustrate the understanding of the functional units of a computer.                               |

| C206.2 | Ability to Identify the different types of instructions.                                                     |

| C206.3 | Ability to illustrate signal space representation of signal using Gram Schmidt orthonormalisation procedure. |

| C206.4 | Ability to understand the various addressing modes.                                                          |

| C206.5 | Ability to understand the I/O addressing system.                                                             |

| C206.6 | Ability to Categorize the different types of memories.                                                       |

# MAPPING OF COURSE OUTCOMES WITH PROGRAM OUTCOMES

| CO'S   | PO1 | PO2 | PO3 | PO4 | PO5 | PO6 | PO7 | PO8 | PO9 | PO10 | PO11 | PO12 |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|

| C206.1 |     |     | 3   |     |     |     |     |     |     |      |      | 1    |

| C206.2 | 2   | 3   | 3   |     | 2   |     |     | 2   |     |      |      | 1    |

| C206.3 | 2   | 3   | 3   | 3   | 2   | 3   | 2   |     |     |      | 2    | 1    |

| C206.4 |     | 3   | 3   | 3   |     | 3   |     |     |     |      |      | 1    |

| C206.5 |     |     | 3   |     | 2   |     |     |     |     |      |      | 1    |

| 2066   |     |     | 3   | 3   |     |     | 2   |     |     |      |      | 1    |

| C206   | 2   | 3   | 3   | 3   | 2   | 3   | 2   | 2   |     |      | 2    | 1    |

| CO'S   | PSO1 | PSO2 | PSO3 |

|--------|------|------|------|

| C206.1 |      |      |      |

| C206.2 | 3    |      |      |

| C206.3 | 3    | 3    | 2    |

| C206.4 | 3    | 3    | 2    |

| C206.5 |      |      |      |

| C206.6 |      |      |      |

| C206   | 3    | 3    | 2    |

#### **SYLLABUS**

| Course code | Course Name           | L-T-P -<br>Credits | Year of<br>Introduction |

|-------------|-----------------------|--------------------|-------------------------|

| EC206       | COMPUTER ORGANISATION | 3-0-0-3            | 2016                    |

**Prerequisite:** EC207 Logic Circuit Design

# **Course Objectives**

- To impart knowledge in computer architecture.

- To impart knowledge in machine language programming.

To develop understanding on I/O accessing techniques and memory structures.

#### **Syllabus**

Functional units of a computer, Arithmetic circuits, Processor architecture, Instructions and addressing modes, Execution of program, Micro architecture design process, Design of data path and control units, I/O accessing techniques, Memory concepts, Memory interface, Cache and Virtual memory concepts.

# Expected outcome.

The students will be able to:

- i. Understand the functional units of a computer

- ii. Identify the different types of instructions

- iii. Understand the various addressing modes

- iv. Understand the I/O addressing system

- v. Categorize the different types of memories

#### **Text Books:**

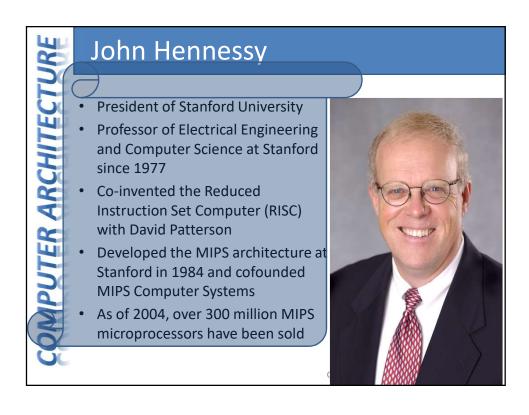

- **1.** David A. Patterson and John L. Hennessey, Computer Organisation and Design, Fourth Edition, Morgan Kaufmann

- **2.** David Money Harris, Sarah L Harris, Digital Design and Computer Architecture, M Kaufmann Elsevier, 2009

#### References

- 1. Carl Hamacher: "Computer Organization", Fifth Edition, Mc Graw Hill

- 2. John P Hayes: "Computer Architecture and Organisation", Mc Graw Hill

- 3. William Stallings: "Computer Organisation and Architecture", Pearson Education

- 4. Andrew S Tanenbaum: "Structured Computer Organisation", Pearson Education

- 5. Craig Zacker: "PC Hardware: The Complete Reference", TMH

#### Course Plan

| Module | Contents                                                                                                                                                                               | Hours | Sem.<br>Exam<br>Marks |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------|

| I      | Functional units of a computer<br>Arithmetic Circuits: Adder-carry propagate adder, Ripple carry<br>adder, Basics of carry look ahead and prefix adder, Subtractor,<br>Comparator, ALU | 4     | 15%                   |

|        | Shifters and rotators, Multiplication, Division                                                                                                                                        | 3     | ]                     |

|        | Number System: Review of Fixed point & Floating point number system                                                                                                                    | 1     |                       |

| II     | Architecture: Assembly Language, Instructions, Operands, Registers, Register set, Memory, Constants                                                                                    | 2     | 15%                   |

|        | Machine Language: R-Type, I-Type, J-Type Instructions, Interpreting machine language code                                                                                              | 3     | 1370                  |

|        | FIRST INTERNAL EXAMINATION                                                                                                                                                             |       |                       |

| III    | MIPS Addressing modes – Register only, Immediate, Base, PC-relative, Pseudo - direct                                                                                                   | 3     | 15%                   |

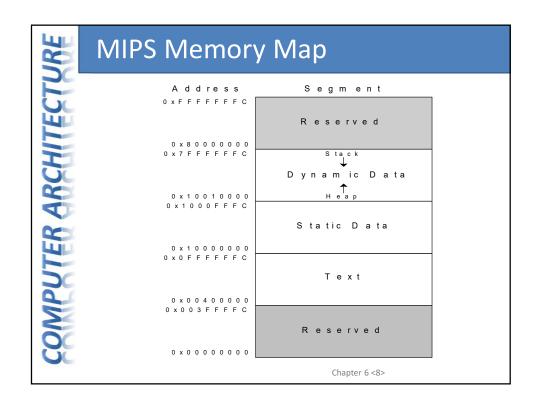

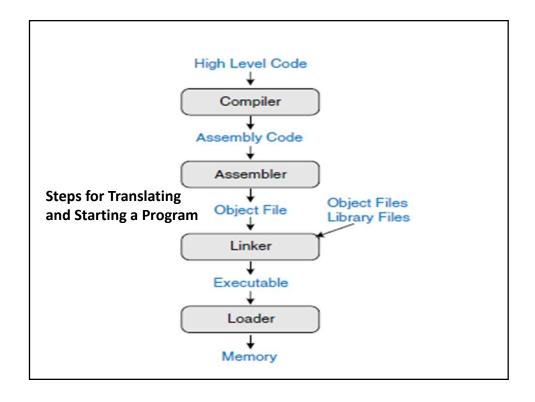

|    | MIPS memory map, Steps for executing a program - Compilation, Assembling, Linking, Loading                                                                    | 3 |     |  |  |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|--|--|

|    | Pseudo instructions, Exceptions, Signed and Unsigned instructions, Floating point instructions                                                                | 3 |     |  |  |

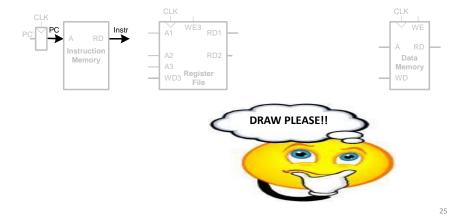

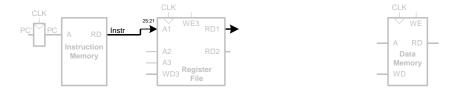

|    | MIPS Microarchitectures – State elements of MIPS processor                                                                                                    | 1 | 15% |  |  |

| IV | Design process and performance analysis of Single cycle processor, Single cycle data path, Single cycle control for R – type arithmetic/logical instructions. | 3 |     |  |  |

|    | Design process and performance analysis of multi cycle processor, Multi cycle data path, Multi cycle control for R – type arithmetic/logical instructions.    | 3 |     |  |  |

| v  | I/O system – Accessing I/O devices, Modes of data transfer, Programmed I/O, Interrupt driven I/O, Direct Memory Access, Standard I/O interfaces – Serial port, Parallel port, PCI, SCSI, and USB.               | 3 | 20  |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|

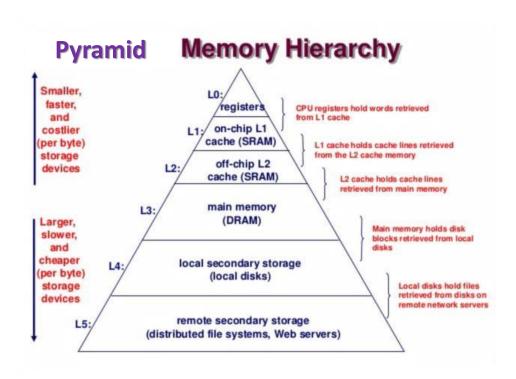

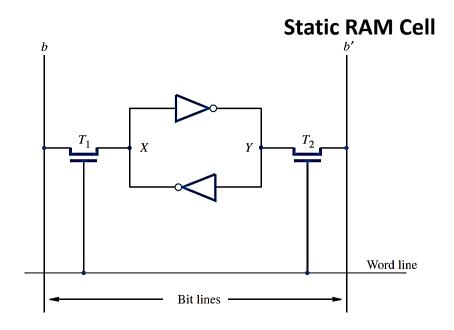

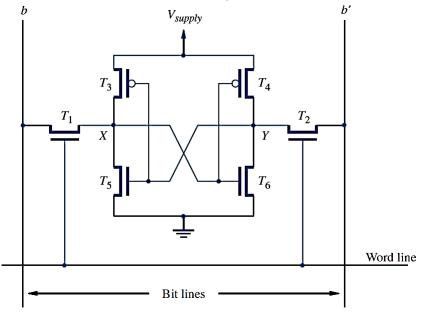

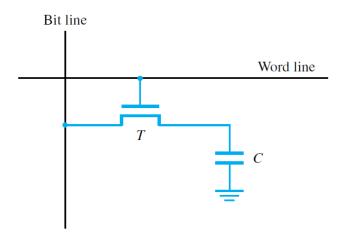

| •  | Memory system — Hierarchy, Characteristics and Performance analysis, Semiconductor memories (RAM, ROM, EPROM Memory Cells — SRAM and DRAM, internal organization of memory chip, Organization of a memory unit. | 4 |     |

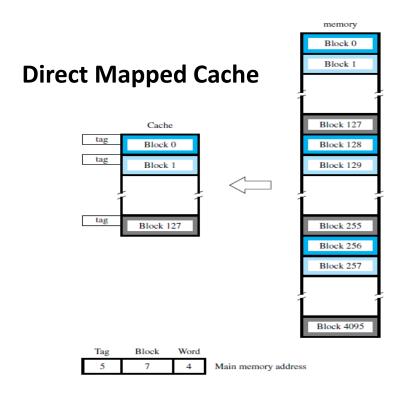

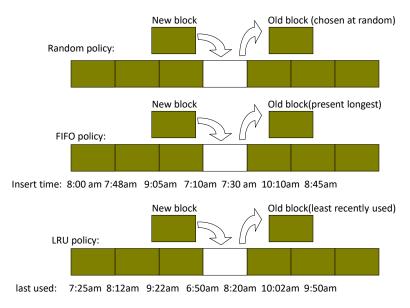

| VI | Cache Memory – Concept/principle of cache memory, Cache size, mapping methods – direct, associated, set associated, Replacement algorithms. Write policy- Write through, Write back.                            | 3 | 20% |

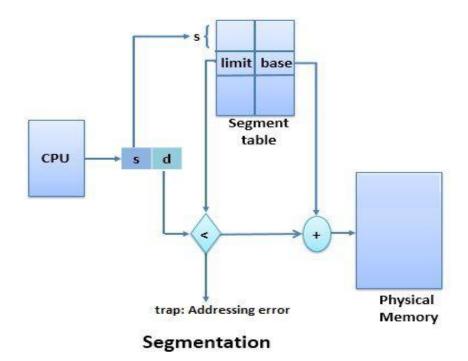

|    | Virtual Memory – Memory management, Segmentation, Paging,<br>Address translation, Page table, Translation look aside buffer.<br>END SEMESTER EXAM                                                               | 3 |     |

# **Question Paper Pattern (End Sem Exam)**

Maximum Marks: 100 Time: 3 hours

The question paper shall consist of three parts. Part A covers modules I and II, Part B covers modules III and IV, and Part C covers modules V and VI. Each part has three questions uniformly covering the two modules and each question can have maximum four subdivisions. In each part, any two questions are to be answered. Mark patterns are as per the syllabus with maximum80 % for theory and 20% for logical/numerical problems, derivation and proof.

#### QUESTION BANK

# **Module-1**:

- **1.** Perform the following shift operations on <u>8-bit binary representations</u> of the decimal numbers and hence verify the shift rules (wherever applicable):

- (a) 4 << 4 (b) 16 << 2 (c) -32 >>> 4 (d) 64 >> 4 (e) 64 >> 2 (f) 32 << 0.5

- **2.** Implement a two Operand 8-bit Equality Comparator for the numbers A and B represented in 8-bit binary. State the rule for the operations.

- **3.** Implement a 32-bit *Carrylookahead Adder*, starting from the 4-bit Adder. Clearly depict the logic diagrams with the supporting analyses. Compute the overall delay of the Adder.

- **4.** From first principles, construct a *Carry Prefix Adder* with logic diagram and supporting analyses. Estimate the delay of the Adder.

- **5.** Implement a 32-bit Adder using Ripple Carry Adder. Explain operation. Estimate the total delay.

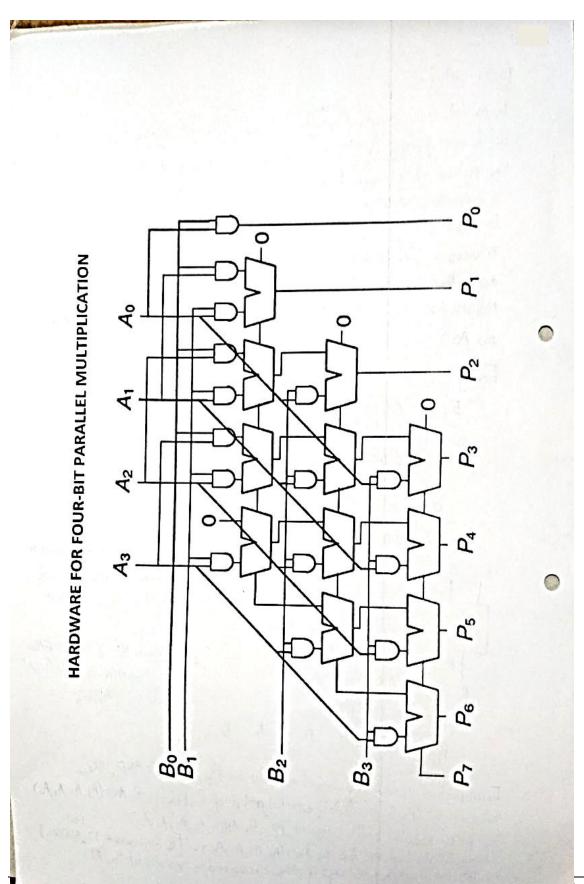

- **6.** Construct an 8-bit Array Multiplier to handle 8-bit Multiplicand and 8-bit Multiplier, with the aid of a supporting binary example of the multiplication process. Estimate the delay of the Multiplier.

- **7.** Construct a *non-restoring Divider* as a Sequential circuit with the aid of a supporting example of division and the control flow process for the operation.

- **8.** Construct a *Multiplier* as a Sequential circuit with the aid of a supporting example of multiplication and the control flow process for the operation.

- **9.** Perform the implementation of 4-bit Rotators for ROL and ROR operations on an 4-bit operands A to yield Y, with proper use of the shamt bits.

- **10.** Represent the two decimal numbers 7.875 and 0.1875 in the *IEEE 754 standard single* precision floating point number format and perform the Addition of the numbers with final representation of the result in the same format.

- **11.** Perform the implementation of 4-*bit Shifters* for LSL, LSR and ASR operations on an 4-bit operands A to yield Y, with proper use of the shamt bits.

- **12.** Implement a two Operand *4-bit Magnitude Comparator* for the numbers A and B represented in 4-bit binary. State the rules for the operation.

- **13.** Examine the operation of a modern Subtractor with the aid of a sketch and hardware details.

- **14.** Construct an eight-bit Equality Comparator from first principles and list the hardware requirements. Does it validate the three Y's?

- **15.** Investigate the operation of a 4-bit Shifter with the aid of hardware representation diagram with wirings for left shift, logical right shift and arithmetic right shift. How the wiring would be tweaked to support Rotator?

- **16.** Examine the Functional Units of a Computer with the aid of a sketch and hardware details.

- **17.** Compare and Contrast RISC and CISC in the context of Computer Architectures, with the help of examples.

- **18.** Investigate the hardware of the ALU Implementation with symbol, functional table and internal structure. Verify its adaptability in the context of modern computing.

- **19.** Investigate the operation of an 8-bit Shifter with the aid of hardware representation diagram for left shift, logical right shift and arithmetic right shift. How does it support Rotation operation?

- **20.** Give definitions of Computer Organization, Computer Architecture and Computer Hardware. State examples of Computers.

- **21.** Perform the following operations using 8-bit binary representations and justify the shift rules: 16 << 2; -32>>>4;

- **22.** Investigate the operation of the Carry Look Ahead Adder with the help of logic diagrams. Calculate the delay for this Adder and compare with that of Ripple Carry Adder.

- **23.** Compare the delays of a 32-bit ripple carry adder and a 32-bi5 carry look ahead adder with 4-bit blocks. Assume each 2-i/p gate delay is 200ps and the FA delay is 400ps.

# Module 1 and 2

- **1.** With the help of a block diagram, describe the structure and functional operation of an Digital Computer.

- **2.** Write short notes on:

- a. Differences between RAM and ROM

- **b.** Computer Hardware

- **c.** Computer Architecture

- **d.** Assembly language and its relevance in the context of Computer Architecture

- **e.** Logical Implementation of a Full Adder from Truth Table, K-Map Minimizations and diagram.

- f. Internal Registers of the Processor and their functions

- **3.** Describe the principle and operation of Ripple Carry Adder with the aid of circuit diagram and proper design. Estimate the delay in this circuit.

- **4.** Perform the following shift operations on <u>8-bit binary representations</u> of the decimal numbers and hence verify the shift rules (wherever applicable):

- (b) 4 << 4 (b) 16 << 2 (c) -32 >>> 4 (d) 64 >> 4 (e) 64 O>> 2 (f) 32 << O 5

- **5.** Describe the principle and operation of Carry Lookahead Adder with the aid of circuit diagram and proper design. Estimate the delay in this circuit.

- **6.** Compare and contrast Ripple Carry Adder with Carry Lookahead Adder.

- 7. Describe the implementation of a 4-bit Multiplier using Array Multiplier with the aid of all appropriate diagrams and supporting analyses. State the hardware requirements for n-bit multiplication.

- **8.** Describe the implementation of a 4-bit Multiplier using Sequential Circuit Multiplier with the aid of all appropriate diagrams and supporting analyses. State the hardware requirements for n-bit multiplication.

- **9.** Describe the implementation of a 4-bit Divider using Sequential Circuit Divider with the aid of all appropriate diagrams and supporting analyses.

- **10.** Explain the Shifters and Rotators by simple examples. Discuss the hardware requirements. Implement 4-bit Shifters for logical and arithmetic operations.

- 11. Provide the logical implementation of the ALU with the aid of supporting analyses, functional table and internal representation. Describe its operations. Suggest how Flags could be made available.

- **12.** Explain the Comparator circuit used in the Processor with implementation for the different types. Choose 4-bit operands for your answer.

- **13.** Describe how a Subtractor can be implemented in modern fast arithmetic circuits. Use appropriate logic diagrams and other representations.

- **14.** Estimate the delay of a 64-bit carry prefix adder assuming that each 2-input Gate has a delay of 400 ps.

- **15.** With the help of suitable examples, differentiate between the R-type and I-type Instructions in MIPS machine language.

- **16.** Illustrate the IEEE standard for single precision and double precision floating point numbers.

- **17.** Write short notes on:

- a. MIPS Register Set.

- b. Byte Addressable Memory.

- c. Format of J-Instructions in MIPS machine language

- **18.** Assume that opcode 'addi' is represented by  $8_{10}$ , register 'add' function is represented by the function code  $32_{10}$ , and register s0 to s7 are represented by  $16_{10}$  to  $23_{10}$ , in MIPS Machine language.

- a. Translate the following machine language code into MIPS assembly language: 0x2237FFF3

- b. Translate the following MIPS assembly code into MIPS machine code in hex format: add \$s0, \$s4, \$s5

- **19.** Describe the structure of the N-bit Non-restoring Divider as a sequential circuit with the help of appropriate logic diagram and illustrations with analyses.

- 20. Translate the following high-level code into assembly language. Assume variables a to c are held in registers \$s0 to \$s2 and f to j are in \$s3 to \$s7.

$$a = b - c;$$

$f = (q + h) - (i + j);$

**21.** Describe the types of Digital Computers and the factors involved in comparing their performance.

**22.** Investigate how the arithmetic operations of Addition/Subtraction and Multiplication are performed on floating point operands within the Processor.

#### Module 3 and 4

- **23.** Describe the Addressing Modes of the MIPS with the aid of examples of Instructions for each type.

- **24.** What is meant by Microarchitecture? Explain the relevance with regards to MIPS architecture.

- **25.** Explain the Performance Analysis of Computer systems.

- **26.** Explain the MIPS Memory Map with the help of a diagram, stating lucidly the various sections or segments and their properties and functions.

- **27.** With the aid of a diagram, describe the steps involved in translating and executing a high level language program.

- **28.** Describe the Pseudo-instructions used in MIPS architecture with the help of four examples. Decompose the same into legitimate MIPS instructions.

- **29.** Describe the concept of Exception Processing and its implementation in MIPS architecture.

- **30.** Explain the signed and unsigned instructions of the MIPS for different categories of Instructions with the aid of lucid examples.

- **31.** Describe the Floating Point Instructions of the MIPS architecture with the help of examples of instructions and their usage.

- **32.** Compare and contrast the three microarchitectures used for MIPS architecture.

- **33.** Derive the expression for Cycle Time in a Single Cycle MIPS processor. If the Cycle time for a single cycle MIPS processor is 1000 pS, calculate the total execution time for a program with 10 lakh instructions.

- **34.** List the main drawbacks of Single Cycle Microarchitecture. How are they eliminated in Multi Cycle Microarchitecture?

- **35.** With the help of suitable examples, differentiate between the R-type and I-type Instructions in MIPS machine language.

- **36.** Illustrate the IEEE standard for single precision and double precision floating point numbers.

- **37.** Write short notes on:

- d. MIPS Register Set.

- e. Byte Addressable Memory.

- f. Format of J-Instructions in MIPS machine language

- **38.** Assume that opcode 'addi' is represented by  $8_{10}$ , register 'add' function is represented by the function code  $32_{10}$ , and register s0 to s7 are represented by  $16_{10}$  to  $23_{10}$ , in MIPS Machine language.

- c. Translate the following machine language code into MIPS assembly language: 0x2237FFF3

- d. Translate the following MIPS assembly code into MIPS machine code in hex format: add \$s0, \$s4, \$s5

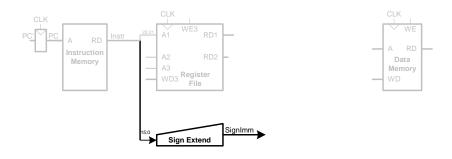

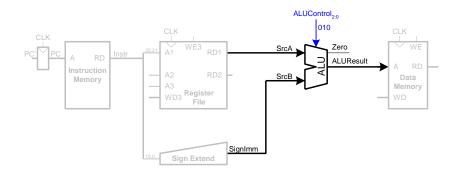

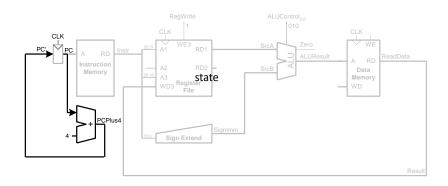

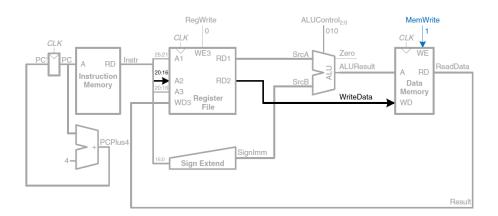

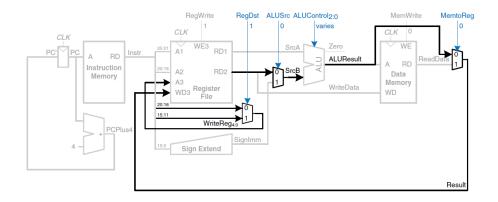

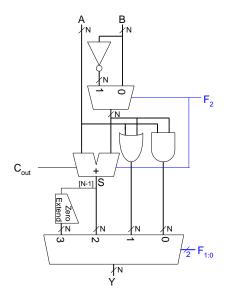

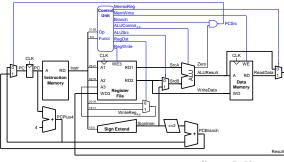

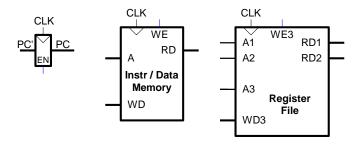

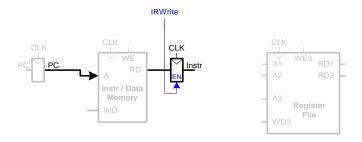

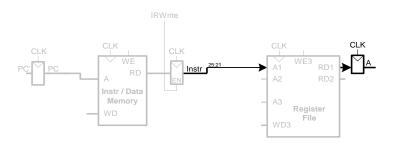

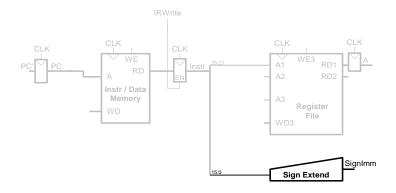

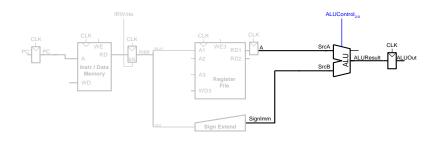

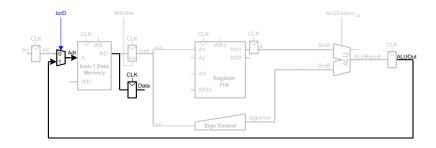

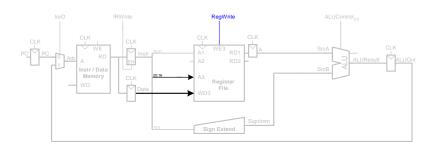

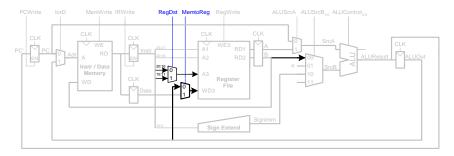

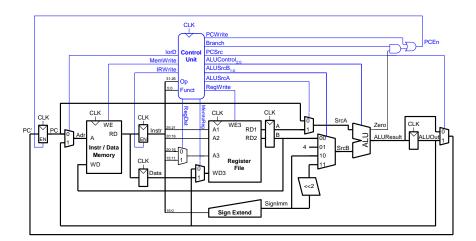

- **39.** Describe the organization of the Datapath of a Single Cycle Microarchitecture for an 1w instruction. Support your answer with the aid of diagrams of the interconnections between the State Elements.

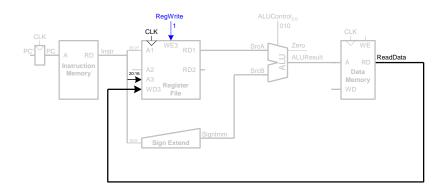

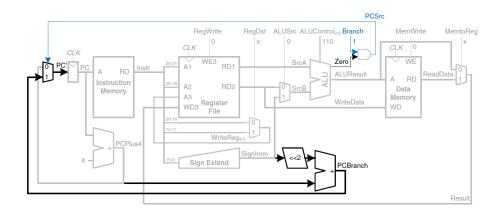

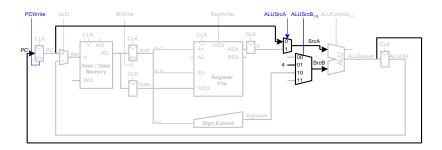

- **40.** Describe the organization of the enhanced or extended Datapath of a Single Cycle Microarchitecture for inclusion of sw instruction, R-type instructions and beq instructions. Support your answer with the aid of diagrams of the interconnections between the State Elements.

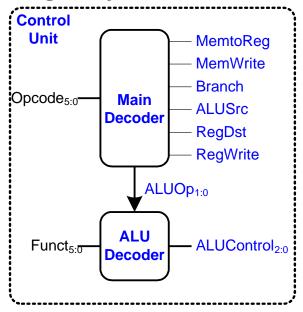

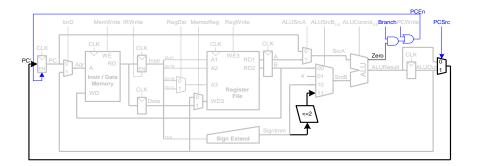

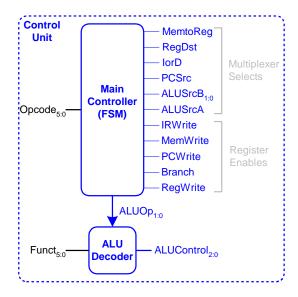

- **41.** Describe the organization of the Control unit of a Single Cycle Microarchitecture for an lw instruction and extend the same for the other categories of Instructions.

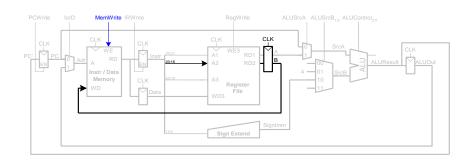

- **42.** Describe the organization of the Datapath of a Multi Cycle Microarchitecture for an lw instruction and other categories of Instructions. Support your answer with the aid of diagrams of the interconnections between the State Elements.

- **43.** Describe the organization of the Control Unit of a Multi Cycle Microarchitecture for an lw instruction and other categories of Instructions. Support your answer with the aid of diagrams of the interconnections between the State Elements.

- **44.** Derive the expression for CPI (M) and Cycle Time in a Multi Cycle MIPS processor. If the Cycle time for a multi cycle MIPS processor is 1000 pS, calculate the total execution time for a program with 10 lakh instructions. Compare and contrast this result with that of Single Cycle Microarchitecture.

# **MODULE 5**

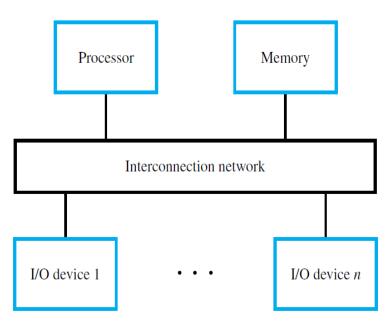

- 1. State the various types of Input and Output devices that need to be used in a modern General purpose or Embedded Computer, and provide details how I/O Capability is provided?

- 2. Explain how accessing I/O devices is made possible in modern Computer, with the aid of a generic sketch.

- 3. Explain the relevance of Memory Mapped I/O.

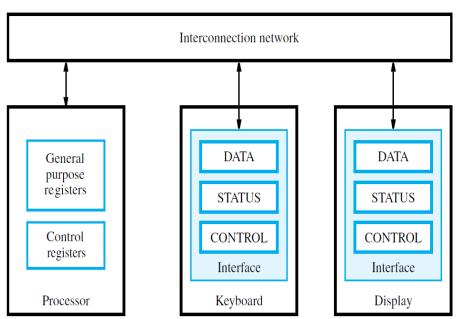

- 4. State the need for I/O Device Interface and illustrate with the aid of a diagram the connections between CPU and I/O devices.

- 5. State the modes of I/O Data Transfer.

- 6. Explain Programmed controlled I/O mechanism.

- 7. Explain Interrupt Driven I/O mechanism with the aid of a diagram.

- 8. What is DMA? How does it use Interrupts?

- 9. Explain the DMA Controller Registers with the aid of diagrams.

- 10. Describe the DMA transfer with the aid of diagram and give details of the role of DMA Controller.

- 11. What is a Port and what are the types? Explain.

- 12. Explain functions of I/O Interface.

- 13. What is the need for a standard for I/O device connections?

- 14. Describe the objectives of USB and provide technical details of the standard.

- 15. Describe PCI Bus with the aid of diagram and give its advantages and benefits.

- 16. Investigate the SCSI Bus and how its serves the purpose of efficient data transfer, with details of a typical read operation.

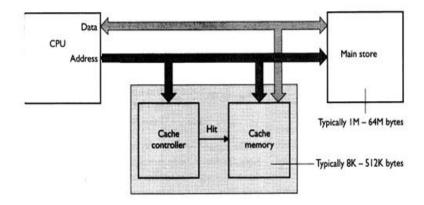

- 17. Investigate Memory Hierarchy with the aid of a diagram and provide details of the different layers.

- 18. Explain the characteristics of Memory.

- 19. Describe Static Memories with the aid of diagrams.

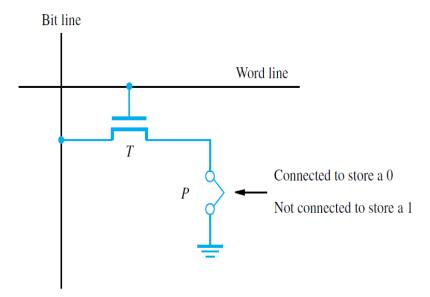

- 20. Describe Dynamic RAM with the aid of a diagram.

- 21. Provide the internal organization of a Dynamic Memory Chip with a diagram.

- 22. Compare and Contrast Asynchronous and Synchronous DRAMs.

- 23. Explain the relevance of SIMMs and DIMMs in modern Computer Systems.

- 24. Compare and Contrast RAM and ROM by providing their inherent characteristics and differences.

- 25. With the aid of a diagram, explain the ROM Cell.

- 26. Explain PROM, EPROM and EEPROM.

- 27. Describe Flash memory and Flash Cards.

- 28. Compare and Contrast Flash Drives and Hard Disk Drives.

# **MODULE 6**

- 1. State and explain the Principle of Locality.

- 2. State and explain the Locality of Reference.

- **3.** Describe the Role of Cache memory w.r.t Memory Hierarchy.

- **4.** With a diagram explain the Cache Memory Organization.

- 5. Define Cache Hit and Miss.

- **6.** Explain the Cache Read process.

- 7. Compare the Cache Write- Write Through and Write Back a.k.a Copy back mechanism.

- **8.** Define Cache Hit Rate ,Miss Rate, Ave Mem Access Time (AMAT)

- **9.** Perform Cache Hit Rate ,Miss Rate, AMAT Calculations ( Refer worked out questions in notes)

- **10.** What is meant by Mapping and Replacement?

- 11. Perform an Analysis of Direct Mapped Cache or Direct Mapping with the aid of diagram.

- **12.** Perform an Analysis of Associative Cache Mapping with the aid of diagram.

- 13. Perform an Analysis of Set Associative Cache Mapping with the aid of diagram.

- **14.** Explain the use of Write Buffer.

- **15.** Perform an Analysis of Replacement Algorithms.

- **16.** Compare the complexity of implementation of the replacement algorithms.

- **17.** Explain the need for Virtual Memory in Computers.

- **18.** Analyze the Virtual Memory Organization with the help of a diagram.

- **19.** Explain the Virtual Address or Logical Address.

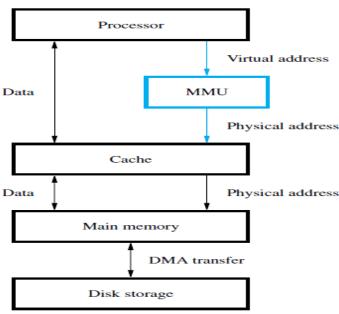

- **20.** Describe the Memory Management Unit (MMU) with a diagram.

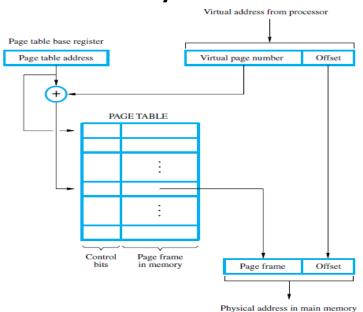

- **21.** Describe the Address Translation mechanism.

- 22. Explain the Virtual Memory Address Translation

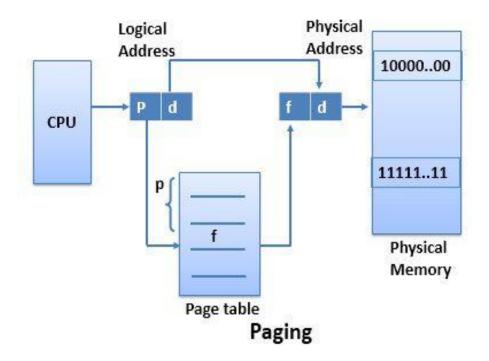

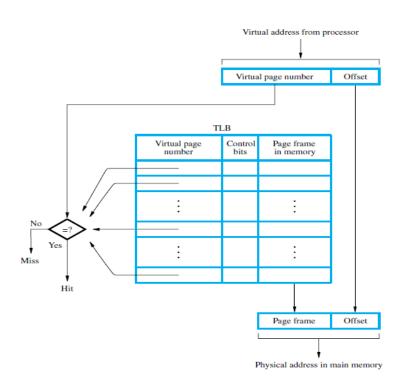

23. Describe Paging with diagram. 24. Describe Translational Look aside Buffer (TLB) with diagram. **25.** Explain Page Faults. **26.** Describe the Segmentation with the help of a diagram. 27. Compare and contrast Paging and Segmentation.

# **Introduction to Computer Organization**

**Computer Organization** is concerned with the function and design of the various units or sections of Digital Computers, that store and process information, receive information from external sources and send computed results to external destinations.

**Computer Architecture** encompasses the specification of an Instruction Set and the hardware units that implement Instructions.

**Computer Hardware** consists of Electronic circuits, Displays, Electronic, magnetic and optical storage media, Electromechanical equipment and Communication facilities.

**Computer Software** is concerned with the System Software or Operating System that manages the Hardware as well as the Application Software as well as Programming languages and Utilities.

**Digital Computer** is a fast Electronic Calculating Machine that accepts digitize input information, processes it according to a list of internally stored Instructions, and produces resulting output information. The list of instructions is called computer program and the internal storage is computer memory.

# **Computer Types**

Since their introduction in the 1940s, digital computers have evolved into many different types that vary widely in size, cost, computational power, and intended use. Modern computers can be divided roughly into four general categories:

- *Embedded computers* are integrated into a larger device or system in order to automatically monitor and control a physical process or environment. They are used for a specific purpose rather than for general processing tasks. Typical applications include industrial and home automation, appliances, telecommunication products, and vehicles. Users may not even be aware of the role that computers play in such systems.

- Personal computers have achieved widespread use in homes, educational institutions, and business and engineering office settings, primarily for dedicated individual use. They support a variety of applications such as general computation, document preparation, computer-aided design, audiovisual entertainment, interpersonal communication, and Internet browsing. A number of classifications are used for personal computers.

Desktop computers serve general needs and fit within a typical personal workspace.

Workstation computers offer higher computational capacity and more powerful graphical display capabilities for engineering and scientific work.

Finally, *Portable* and *Notebook computers* provide the basic features of a personal computer in a smaller lightweight package. They can operate on batteries to provide mobility.

- Servers and Enterprise systems are large computers that are meant to be shared by a potentially large number of users who access them from some form of personal computer over a public or private network. Such computers may host large databases and provide information processing for a government agency or a commercial organization.

- Supercomputers and Grid computers normally offer the highest performance. They are the most expensive and physically the largest category of computers. Supercomputers are used for the highly demanding computations needed in weather forecasting, engineering design and simulation, and scientific work. They have a high cost. Grid computers provide a more cost-effective alternative. They combine a large number of personal computers and disk storage units in a physically distributed high-speed network, called a grid, which is managed as a coordinated computing resource. By evenly distributing the computational workload across the grid, it is possible to achieve high performance on large applications ranging from numerical computation to information searching.

There is an emerging trend in access to computing facilities, known as *cloud computing*. Personal computer users access widely distributed computing and storage server resources for individual, independent, computing needs. The Internet provides the necessary communication facility. Cloud hardware and software service providers operate as a utility, charging on a pay-as-you-use basis.

# FUNCTIONAL UNITS OF A COMPUTER

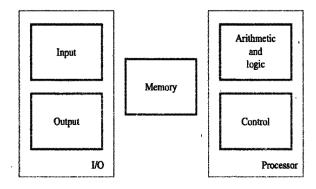

Figure 1.1 Basic functional units of a computer.

A computer consists of five functionally independent main parts: input, memory, arithmetic and logic, output, and control units, as shown in Figure 1.1. The input unit accepts coded information from human operators, from electromechanical devices such as keyboards, or from other computers over digital communication lines. The information received is either stored in the computer's memory for later reference or immediately used by the arithmetic and logic circuitry to perform the desired operations. The processing steps are determined by a program stored in the memory. Finally, the results are sent back to the outside world through the output unit. All of these actions are coordinated by the control unit. Figure 1.1 does not show the connections among the functional units. These connections, which can be made in several ways, are discussed throughout this book. We refer to the arithmetic and logic circuits, in conjunction with the main control circuits, as the *processor*, and input and output equipment is often collectively referred to as the *input-output* (I/O) unit.

We now take a closer look at the information handled by a computer. It is convenient to categorize this information as either instructions or data. *Instructions*, or *machine* instructions, are explicit commands that

- Govern the transfer of information within a computer as well as between the computer and its I/O devices

- Specify the arithmetic and logic operations to be performed

A list of instructions that performs a task is called a *program*. Usually the program is stored in the memory. The processor then fetches the instructions that make up the program from the memory, one after another, and performs the desired operations. The computer is completely controlled by the *stored program*, except for possible external interruption by an operator or by I/O devices connected to the machine.

Data are numbers and encoded characters that are used as operands by the instructions. The term data, however, is often used to mean any digital information. Within this definition of data, an entire program (that is, a list of instructions) may be considered as data if it is to be processed by another program. An example of this is the task of compiling a high-level language source program into a list of machine instructions constituting a machine language program, called the object program. The source program is the input data to the compiler program which translates the source program into a machine language program.

Information handled by a computer must be encoded in a suitable format. Most present-day hardware employs digital circuits that have only two stable states, ON and OFF (see Appendix A). Each number, character, or instruction is encoded as a string of binary digits called bits, each having one of two possible values, 0 or 1. Numbers are usually represented in positional binary notation, as discussed in detail in Chapters 2 and 6. Occasionally, the binary-coded decimal (BCD) format is employed, in which each decimal digit is encoded by four bits.

Alphanumeric characters are also expressed in terms of binary codes. Several coding schemes have been developed. Two of the most widely used schemes are ASCII (American Standard Code for Information Interchange), in which each character is represented as a 7-bit code, and EBCDIC (Extended Binary-Coded Decimal Interchange Code), in which eight bits are used to denote a character. A more detailed description

#### **Input Unit**

Computers accept coded information through input units. The most common input device is the keyboard. Whenever a key is pressed, the corresponding letter or digit is automatically translated into its corresponding binary code and transmitted to the processor.

Many other kinds of input devices for human-computer interaction are available, including the touchpad, mouse, joystick, and trackball. These are often used as graphic input devices in conjunction with displays. Microphones can be used to capture audio input which is then sampled and converted into digital codes for storage and processing. Similarly, cameras can be used to capture video input. Digital communication facilities, via the Internet, can also provide input to a computer from other computers and database servers.

# **Memory Unit**

The function of the memory unit is to store programs and data. There are two classes of storage, called primary and secondary.

#### **Primary Memory**

Primary memory, also called main memory, is a fast memory that operates at electronic speeds. Programs must be stored in this memory while they are being executed. The memory consists of a large number of semiconductor storage cells, each capable of storing one bit of information. These cells are rarely read or written individually. Instead, they are handled in groups of fixed size called words. The memory is organized so that one word can be stored or retrieved in one basic operation. The number of bits in each word is referred to as the word length of the computer, typically 16, 32, or 64 bits.

To provide easy access to any word in the memory, a distinct *address* is associated with each word location. Addresses are consecutive numbers, starting from 0, that identify successive locations. A particular word is accessed by specifying its address and issuing a control command to the memory that starts the storage or retrieval process.

Instructions and data can be written into or read from the memory under the control of the processor. It is essential to be able to access any word location in the memory as quickly as possible. A memory in which any location can be accessed in a short and fixed amount of time after specifying its address is called a *random-access memory* (RAM). The time required to access one word is called the *memory access time*. This time is independent of the location of the word being accessed. It typically ranges from a few nanoseconds (ns) to about 100 ns for current RAM units.

#### **Cache Memory**

As an adjunct to the main memory, a smaller, faster RAM unit, called a *cache*, is used to hold sections of a program that are currently being executed, along with any associated data. The cache is tightly coupled with the processor and is usually contained on the same integrated-circuit chip. The purpose of the cache is to facilitate high instruction execution rates.

#### **Secondary Storage**

Although primary memory is essential, it tends to be expensive and does not retain information when power is turned off. Thus additional, less expensive, permanent *secondary storage* is used when large amounts of data and many programs have to be stored, particularly for information that is accessed infrequently. Access times for secondary storage are longer than for primary memory. A wide selection of secondary storage devices is available, including *magnetic disks*, *optical disks* (DVD and CD), and *flash memory devices*.

# **Arithmetic and Logic Unit**

Most computer operations are executed in the *arithmetic and logic unit* (ALU) of the processor. Any arithmetic or logic operation, such as addition, subtraction, multiplication, division, or comparison of numbers, is initiated by bringing the required operands into the processor, where the operation is performed by the ALU. For example, if two numbers located in the memory are to be added, they are brought into the processor, and the addition is carried out by the ALU. The sum may then be stored in the memory or retained in the processor for immediate use.

When operands are brought into the processor, they are stored in high-speed storage elements called *registers*. Each register can store one word of data. Access times to registers are even shorter than access times to the cache unit on the processor chip.

#### **Output Unit**

The output unit is the counterpart of the input unit. Its function is to send processed results to the outside world. A familiar example of such a device is a *printer*. Most printers employ either photocopying techniques, as in laser printers, or ink jet streams. Such printers may generate output at speeds of 20 or more pages per minute. However, printers are mechanical devices, and as such are quite slow compared to the electronic speed of a processor.

Some units, such as graphic displays, provide both an output function, showing text and graphics, and an input function, through touchscreen capability. The dual role of such units is the reason for using the single name *input/output* (I/O) unit in many cases.

#### **Control Unit**

The memory, arithmetic and logic, and I/O units store and process information and perform input and output operations. The operation of these units must be coordinated in some way. This is the responsibility of the control unit. The control unit is effectively the nerve center that sends control signals to other units and senses their states.

I/O transfers, consisting of input and output operations, are controlled by program instructions that identify the devices involved and the information to be transferred. Control circuits are responsible for generating the *timing signals* that govern the transfers and determine when a given action is to take place. Data transfers between the processor and the memory are also managed by the control unit through timing signals. It is reasonable to think of a control unit as a well-defined, physically separate unit that interacts with other parts of the computer. In practice, however, this is seldom the case. Much of the control circuitry is physically distributed throughout the computer. A large set of control lines (wires) carries the signals used for timing and synchronization of events in all units.

The operation of a computer can be summarized as follows:

- The computer accepts information in the form of programs and data through an input unit and stores it in the memory.

- Information stored in the memory is fetched under program control into an arithmetic and logic unit, where it is processed.

- Processed information leaves the computer through an output unit.

- All activities in the computer are directed by the control unit.

#### **ARITHMETIC CIRCUITS**

Arithmetic circuits are the central building blocks of computers. Computers and digital logic perform many arithmetic functions: addition, subtraction, comparisons, shifts, multiplication, and division.

#### The Three-Y's

Designers use the three "-y's" to manage complexity: hierarchy, modularity, and regularity. These principles apply to both software and hardware systems.

**Hierarchy** involves dividing a system into modules, then further sub-dividing each of these modules until the pieces are easy to understand.

**Modularity** states that the modules have well-defined functions and interfaces, so that they connect together easily without unanticipated side effects.

**Regularity** seeks uniformity among the modules. Common modules are reused many times, reducing the number of distinct modules that must be designed.

These building blocks are not only useful in their own right, but they also demonstrate the principles of Hierarchy, Modularity, and Regularity. The building blocks are hierarchically assembled from simpler components such as logic gates, multiplexers, and decoders. Each building block has a well-defined interface and can be treated as a black box when the underlying implementation is unimportant. The regular structure of each building block is easily extended to different sizes.

# Addition

Addition is one of the most common operations in digital systems. We first consider how to add two 1-bit binary numbers. We then extend to N-bit binary numbers. Adders also illustrate tradeoffs between speed and complexity.

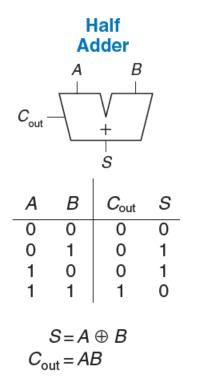

#### Half Adder

We begin by building a 1-bit half Adder. As shown, the half Adder has two inputs, A and B, and two outputs, S and  $C_{out}$ . S is the sum of A and B. If A and B are both 1, S is 2, which cannot be represented with a single binary digit. Instead, it is indicated with a carry out  $C_{out}$  in the next column. The half Adder can be built from an XOR gate and an AND gate.

In a multi-bit Adder,  $C_{out}$  is added or carried in to the next most significant bit. For example, the carry bit is the output  $C_{out}$  of the first column of 1-bit addition and the input  $C_{in}$  to the second column of addition. However, the half Adder lacks a  $C_{in}$  input to accept  $C_{out}$  of the previous column.

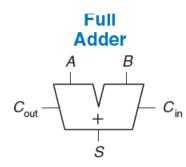

# **Full Adder**

A full Adder accepts the carry in  $C_{in}$  as shown. The figure also shows the output equations for S and  $C_{out}$ .

$$S = A \oplus B \oplus C_{in}$$

$C_{out} = AB + AC_{in} + BC_{in}$

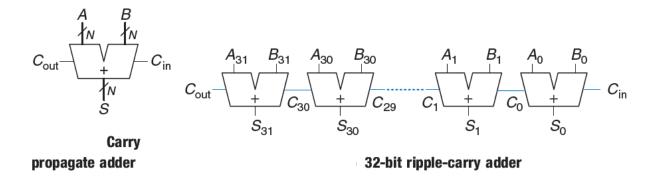

#### **Carry Propagate Adder**

An N-bit Adder sums two N-bit inputs, A and B, and a carry in Cin to produce an N-bit result S and a carry out Cout. It is commonly called a carry propagate Adder (CPA) because the carry out of one bit propagates into the next bit. The symbol for a CPA is shown in Figure 5.4; it is drawn just like a full Adder except that A, B, and S are busses rather than single bits. Three common CPA implementations are called ripple-carry Adders, carry-look ahead Adders, and Prefix Adders.

#### **Ripple-Carry Adder**

The simplest way to build an N-bit carry propagate Adder is to chain together N full Adders. The  $C_{out}$  of one stage acts as the  $C_{in}$  of the next stage, as shown for 32-bit addition. This is called a ripple carry Adder. It is a good application of modularity and regularity: the full Adder module is reused many times to form a larger system. The ripple carry Adder has the disadvantage of being slow when N is large.  $S_{31}$  depends on  $C_{30}$ , which depends on  $C_{29}$ , which depends on  $C_{28}$ , and so forth all the way back to  $C_{in}$ , as shown. We say that the carry ripples through the carry chain. The delay of the Adder, t ripple, grows directly with the number of bits, where  $t_{FA}$  is the delay of a full Adder.

$$t_{\text{ripple}} = Nt_{FA}$$

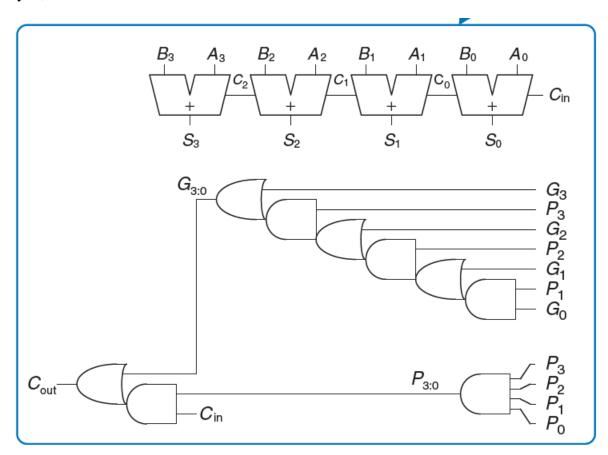

#### Carry-Look Ahead Adder

The fundamental reason that large ripple-carry Adders are slow is that the carry signals must propagate through every bit in the Adder. A carry look ahead Adder (CLA) is another type of carry propagate Adder that solves this problem by dividing the Adder into blocks and providing circuitry to quickly determine the carry out of a block as soon as the carry in is known. Thus it is said to look ahead across the blocks rather than waiting to ripple through all the full Adders inside a block. For example, a 32-bit Adder may be divided into eight 4-bit blocks.

CLAs use generates (G) and propagate (P) signals that describe how a column or block determines the carry out. The ith column of an Adder is said to generate a carry if it produces a carry out independent of the carry in. The ith column of an Adder is guaranteed to generate a carry  $C_i$  if  $A_i$  and  $B_i$  are both 1. Hence  $G_i$ , the generate signal for column i, is calculated as  $G_i = A_i.B_i$ . The column is said to propagate a carry if it produces a carry out whenever there is a carry in. The ith column will propagate a carry in,  $C_{i-1}$ , if either  $A_i$  or  $B_i$  is 1. Thus,  $P_i = A_i + B_i$ . Using these definitions, we can rewrite the carry logic for a particular column of the Adder. The ith column of an Adder will generate a carry out  $C_i$  if it either generates a carry,  $G_i$ , or propagates a carry in,  $P_i.C_{i-1}$ . In equation form,

$$C_i = A_i B_i + (A_i + B_i) C_{i-1} = G_i + P_i C_{i-1}$$

The generate and propagate definitions extend to multiple-bit blocks. A block is said to generate a carry if it produces a carry out independent of the carry in to the block. The block is said to propagate a carry if it produces a carry out whenever there is a carry in to the block. We define  $G_{i:j}$  and  $P_{i:j}$  as generate and propagate signals for blocks spanning columns i through j.

A block generates a carry if the most significant column generates a carry, or if the most significant column propagates a carry and the previous column generated a carry, and so forth. For example, the generate logic for a block spanning columns 3 through 0 is:

$$G_{3:0} = G_3 + P_3(G_2 + P_2(G_1 + P_1G_0))$$

A block propagates a carry if all the columns in the block propagate the carry. For example, the propagate logic for a block spanning columns 3 through 0 is:

$$P_{3:0} = P_3 P_2 P_1 P_0$$

Using the block generate and propagate signals, we can quickly compute the carry out of the block,  $C_i$ , using the carry in to the block,  $C_j$ .

$$C_i = G_{i:i} + P_{i:i}C_i$$

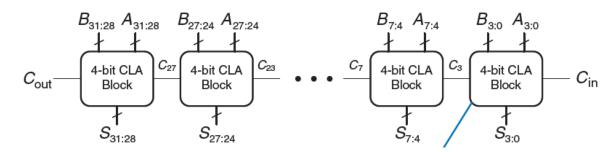

A 32-bit carry-look ahead Adder is composed of eight 4-bit blocks. Each block contains a 4-bit ripple-carry Adder and some look ahead logic to compute the carry out of the block given the carry in, as shown.

The AND and OR gates needed to compute the single-bit generate and propagate signals,  $G_i$  and  $P_i$ , from  $A_i$  and  $B_i$  are left out for brevity. Again, the carry-look ahead Adder demonstrates modularity and regularity.

All of the CLA blocks compute the single-bit and block generate and propagate signals simultaneously. The critical path starts with computing  $G_0$  and  $G_{3:0}$  in the first CLA block.

Cin then advances directly to C<sub>out</sub> through the AND/OR gate in each block until the last.

For a large Adder, this is much faster than waiting for the carries to ripple through each consecutive bit of the Adder. Finally, the critical path through the last block contains a short ripple-carry Adder. Thus, an N-bit Adder divided into k-bit blocks has a delay:

$$t_{CLA} = t_{pg} + t_{pg\_block} + \left(\frac{N}{k} - 1\right) t_{AND\_OR} + k t_{FA}$$

where  $t_{pg}$  is the delay of the individual generate/propagate gates (a single AND or OR gate) to generate Pi and Gi,  $t_{pg\_block}$  is the delay to find the generate/propagate signals  $P_{i:j}$  and  $G_{i:j}$  for a k-bit block, and  $t_{AND\_OR}$  is the delay from  $C_{in}$  to  $C_{out}$  through the final AND/OR logic of the k-bit CLA block. For N >16, the carry-look ahead Adder is generally much faster than the ripple-carry Adder. However, the Adder delay still increases linearly with N.

# Example 1: RIPPLE-CARRY ADDER AND CARRY-LOOKAHEAD ADDER DELAY

Compare the delays of a 32-bit ripple-carry Adder and a 32-bit carry-look ahead Adder with 4-bit blocks. Assume that each two-input gate delay is 100 ps and that a full Adder delay is 300 ps.

<u>Sol</u>:

The propagation delay of the 32-bit ripple carry Adder is  $32 \times 300 \text{ ps} = \underline{9.6 \text{ ns}}$ .

The CLA has  $t_{pg} = 100 \text{ ps}$ ,

$$t_{pg block} = 6 \times 100 \text{ ps} = 600 \text{ ps}, \text{ and}$$

$$t_{AND OR} = 2 \times 100 \text{ ps} = 200 \text{ ps}.$$

The propagation delay of the 32-bit carry-look ahead Adder with 4-bit blocks is:

$$100 \text{ ps} + 600 \text{ ps} + (32/4 - 1) \times 200 \text{ ps} + (4 \times 300 \text{ ps})$$

= 3.3 ns,

**Almost three times faster** than the ripple-carry Adder!

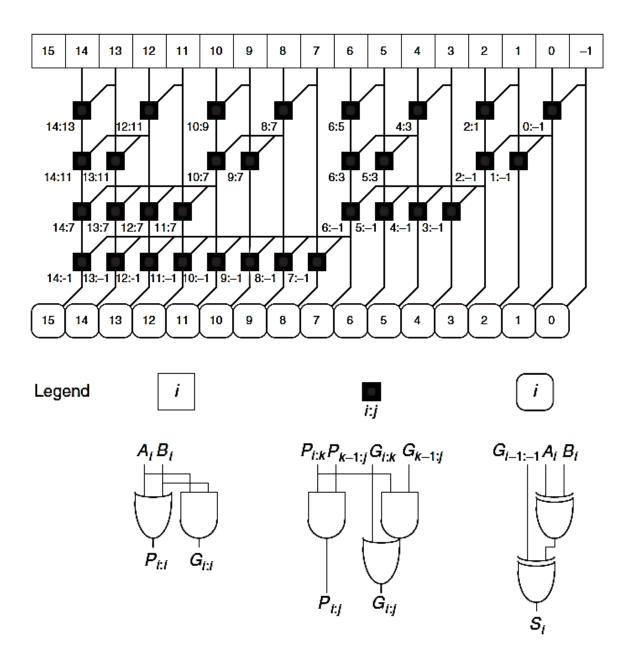

#### **Prefix Adder**

Early computers used ripple carry Adders, because components were expensive and ripple-carry Adders used the least hardware. Virtually all modern PCs use Prefix Adders on critical paths, because transistors are now cheap and speed is of great importance.

Prefix Adders extend the generate and propagate logic of the carry look ahead Adder to perform addition even faster. They first compute G and P for pairs of columns, then for blocks of 4, then for blocks of 8, then 16, and so forth until the generate signal for every column is known. The sums are computed from these generate signals.

In other words, the strategy of a Prefix Adder is to compute the carry in  $C_{i-1}$  for each column i as quickly as possible, then to compute the sum, using

$$S_i = (A_i \oplus B_i) \oplus C_{i-1}$$

Define column i = -1 to hold  $C_{in}$ , so  $G_{-1} = C_{in}$  and  $P_{-1} = 0$ . Then  $C_{i-1} = G_{i-1:-1}$  because there will be a carry out of column i-1 if the block spanning columns i-1 through -1 generates a carry. The generated carry is either generated in column i-1 or generated in a previous column and propagated.

Thus, we rewrite Equation as:

$$S_i = (A_i \oplus B_i) \oplus G_{i-1:-1}$$

Hence, the main challenge is to rapidly compute all the block generate signals  $G_{-1:-1}$ ,  $G_{0:-1}$ ,  $G_{1:-1}$ ,  $G_{2:-1}$ , . . . ,  $G_{N-2:-1}$ . These signals, along with  $P_{-1:-1}$ ,  $P_{0:-1}$ ,  $P_{1:-1}$ ,  $P_{2:-1}$ , . . . ,  $P_{N-2:-1}$ , are called Prefixes.

The diagram shows an N= 16-bit Prefix Adder. The Adder begins with a pre-computation to form  $P_i$  and  $G_i$  for each column from  $A_i$  and  $B_i$  using AND and OR gates.

It then uses  $log_2N=4$  levels of black cells to form the Prefixes of  $G_{i:j}$  and  $P_{i:j}$ . A black cell takes inputs from the upper part of a block spanning bits i:k and from the lower part spanning bits k-1:j. It combines these parts to form generate and propagate signals for the entire block spanning bits i: j using the equations:

$$G_{i:j} = G_{i:k} + P_{i:k}G_{k-1:j}$$

$$P_{i:j} = P_{i:k} P_{k-1:j}$$

A block spanning bits i:j will generate a carry if the upper part generates a carry or if the upper part propagates a carry generated in the lower part. The block will propagate a carry if both the upper and lower parts propagate the carry. Finally, the Prefix Adder computes the sums.

In summary, the Prefix Adder achieves a delay that grows <u>logarithmically</u> rather than linearly with the number of columns in the Adder. This speedup is significant, especially for Adders with 32 or more bits, but it comes at the expense of more hardware than a simple carry-look ahead Adder.

The network of black cells is called a <u>Prefix Tree</u>. The general principle of using Prefix trees to perform computations in time that grows logarithmically with the number of inputs is a powerful technique.

The critical path for an N-bit Prefix Adder involves the pre-computation of P<sub>i</sub> and G<sub>i</sub> followed by log<sub>2</sub>N stages of black Prefix cells to obtain all the Prefixes.

G<sub>i-1:-1</sub> then proceeds through the final XOR gate at the bottom to compute S<sub>i</sub>.

The delay of an N-bit Prefix Adder is:

$$t_{PA} = t_{pg} + \log_2 N(t_{pg\_prefix}) + t_{XOR}$$

where  $t_{pg\_Prefix}$  is the delay of a black Prefix cell.

# Example-2 **PREFIX ADDER DELAY**

Compute the delay of a 32-bit Prefix Adder. Assume that each two-input gate delay is 100 ps.

#### Sol:

The propagation delay of each black Prefix cell t<sub>pg</sub> Prefix is 200 ps (i.e., two gate delays).

Thus, the propagation delay of the 32-bit Prefix Adder is:

$$100 \text{ ps} + \log_2(32) \times 200 \text{ ps} + 100 \text{ ps} = 1.2 \text{ ns},$$

which is about <u>three times faster</u> than the carry-look ahead Adder and <u>eight times faster</u> than the ripple-carry Adder from Example 1.

In practice, the benefits are not quite this great, but Prefix Adders are still much faster than the others.

#### Putting It All Together ...

This section introduced the half Adder, full Adder, and three types of carry propagate Adders: ripple-carry, carry-look ahead, and Prefix Adders. Faster Adders require more hardware and therefore are more expensive and power-hungry. These trade-offs must be considered when choosing an appropriate Adder for a design.

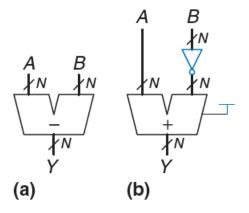

# **Subtraction**

Adders can add positive and negative numbers using two's complement number representation. Subtraction is almost as easy: flip the sign of the second number, then add. Flipping the sign of a two's complement number is done by inverting the bits and adding 1.

To compute Y = A - B, first create the two's complement of B:

Invert the bits of B to obtain B and add 1 to get  $\neg B = B + 1$ .

Add this quantity to A to get Y = A + B + 1 = A - B.

This sum can be performed with a single CPA by adding A + B with  $C_{in} = 1$ .

The symbol for a Subtractor and the underlying hardware for performing Y = A - B are shown.

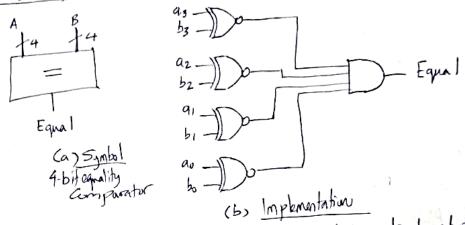

# Comparators:-

A Comparator determines whether two binary numbers are equal or if one is greater or less than the other

A Comparature receives two N-bit binary numbers, A and B.

There are two common types of Comparators

# Equality Comparator! -

An equality comparator produces a single output to include whether A is equal to B (A == B). The implementation first checks to find if conseponding bits of A and B are equal, using XNOR gates. The runkes are equal, if all of the corresponding bits are equal

A magnitude comparator produces one or more outputs to indicate Magnitude Comparator: the relative Values of A and B

Magnitude comparison is above by Computing A-B and looking at the sign (MSB) bit of result as shown. If the result is regative (i.e., Son bit is 1) then A is less than B. Else A isgreater than or equal to 5.

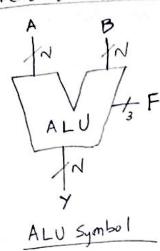

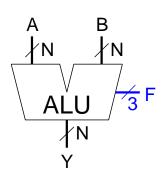

A<B N-bit magnitude comparate Arithmetic Legic Unit (ALU):-

| F2:0   | perations<br>Function |

|--------|-----------------------|

| 000    | A AND B               |

| 001    | A OR B                |

| 010    | A+B                   |

| 011    | Not used              |

| 100    | AMDB                  |

| 101    | A OR B                |

| 10.000 | A-B                   |

| 110    | //                    |

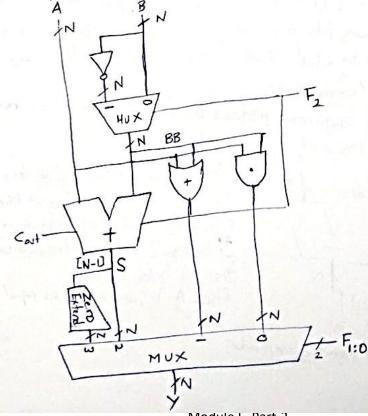

An Arithmetic Logic Unit (ALU) combines a variety of mothematical and logical operations into a single unit and forms the heart of the computer system. The ALU accepts N-bit inputs and outputs. There is a control sismalism F, that specifies which function to perform.

A B

Module I

Module | Part-2

Page 2

The ALU consists of an N-bit Adder, N two-input AND and OR Gades, It has an Inverter and a multiplexer (MUX) to optionally invert input B when the Fz control signal is asserted. A 4:1 Mux chooses the desired function based on the Fig Control signals. The arithmetic and bagial blacks in the ALU operate on A and BB. BB is either B or B, depending on Fz. if Fin = 00, the of Mux chooses A AND B if Fi:0 = 01, the olp Mux chases A OR B if Fio = 10, the of MUX chooses addition or subtraction. Note that Fz is the carry-in to the Adder, as well as control for ilp 2:1 MUX. Also note that B+1 = -B in 2's complement arithmetic. if Fz = 0, the ilp Mux chooses A+B if Fz = 1, the ilp Mux chases A-B (ALV computer A+B+1) if F2:0 = 111, the ALU performs Set Less Than (SLT) operation. When A < B, Y=1 } Y is set to 1 if A is less than B Else Y=0 } SLT is performed by computing S= A-B if S is regative (i.e., the sign bit is 1), A<B The zero extend unit produces an N-bit olp by Concatenating its I bit input with 0's in the most significant bits. The sign bit of S (N-1th bit) is the input to the unit. Some ALUS produce extra signals called Flags. For example, Overflow flag, zero flag etc.

Example: SET LESS THAN

Configure a 32-bit ALU for the SLT operation. Let A = 25 and B = 32Show the control signals and output, Y

501:-

Since AKB, the value of Y is 1.

For SLT , Fz: = 111

With Fz = 1, the adder unit is configured as subtractor.

Outpet 6 = 25-32 = -710

+7,0 = 0 00.011

-710 = 1 11 ... 1001 (2's complement)

With Fire = 11, the output MUX sets Y = S3, = 1

Zero extend unit produces,

Module I Part-2 Page 4

Shifters and Rotators

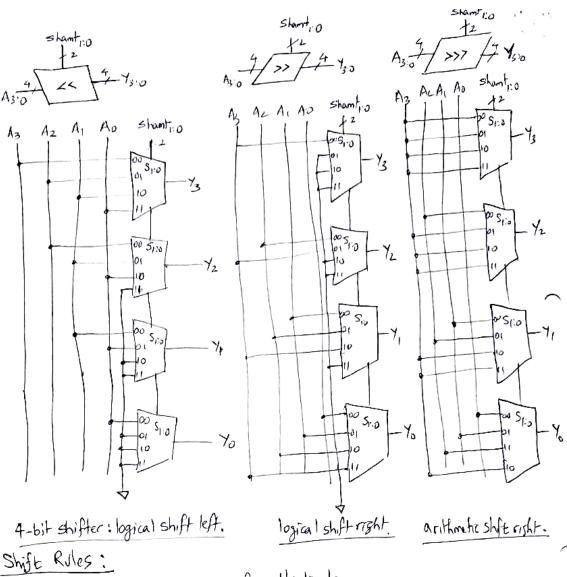

Shifter and Rotators move bits directionally and effectively multiply or divide by powers of 2.

A Shifter shifts a king number left or right by a specified number of positions.

Types of shifters: -

1 Logical shifter: -

Shifts the binary number to the left (LSL) or right (LGR) and fills empty spots with Os.

Example: 11001 LSR 2 = 00110 11001 LSL 2 = 00100

2. Arithmetic Shifter . -

Shifts the same as a logical shifter, but on right shifts, fills the MSB with a copy of the 'old'msb. this is useful for multiplying and dividing sisned numbers. Arithmetic shift left (ASL) is the same as LSL.

Example: 11001 ASR 2 = 11110 11001 ASL 2 = 00100

3. Rotator :-

Rotates number in cirale such that the empty spots are filled with bits shifted off the other end.

Example: 11001 ROR 2 = 01110 11001 ROL 2 = 00111

A N-bit shifter can be built from N, N:1 Multiplexers. The ilp is shifted by 0 to N-1 bits, depending on the value of the log\_N select lines · (shamt) The operators KK, >> and >>> indicate SL, LSR, ASR shantio holds 2-bit shift amount. 4-bit shifter Output 4, receives the input, A shifted by 0 to 3 bits. When shamt, :0 = 00, Y=A.

A left shift is a special case of multiplication.

A left shift by N bits multiplies the number by 2. Example: 000011

# Represent the following numbers as 8-61 bring trang and perform the following shifts.

Validate the answer king the Shift roles

i) +310 < 4

ii) -4,0004

:. 310 × 24 = 4810

Arithmetiz rightshift by N bits divides number by 2N.

Example:  $-11100_2 >>> 2 = 11111_2$ =>  $-410/2^2 = -110$  (show!)

Module I

Module I Part-2

Page 6

## Multiplication:

In multiplication operation of unsigned bring numbers, partial products are formed by multiplying (ANDing) a single bit of the multiplier with the entire multiplicand. Then the shifted partial products are added to form the result.

In general, an NXN Multiplier multiplies two N-bit numbers and produces a 2N-bit result. The partial products in binary multiplication are either the multiplicand or all O's.

Hulfiplication of 1-bit binary numbers is same as the AND operation, so AND gates are used to form the partial products

Example: Show 5 x 7 on paper using binary reprosentation 5x = 0101 × = multiplicand 7 = 0111 × = multiplier 0101 partial products

0101 025 00011 addition of PPs.

A360 A280 A180 A0.80 Ash, Alby A183 A083 P7 P6 P5 P4 P3 P2 P, Po

With N-bit operands there are N partial products and (N-1) stages of Host adders.

Total: N2 2-1/P AND GAIG +N(N-1) 2-1/P (1-6it) ADDERG.

Each partial product is a single multiplier bit (B3,B2,B1980) AND the multidicant bit (As, Az, A1, A0). The partial product of first row is Bo AND (A3, Az, A1, A0) This pp is added to shifted second pp, B, AND (A3, A2, A1, A0). Continue till the last PP for B3 AND (A3, A2, A1, A0). [16 AND Guts+ 12 ADDERS]

ADDERS are needed to sum the Corresponding values of the PPS.

Module I Part-2 Page 8

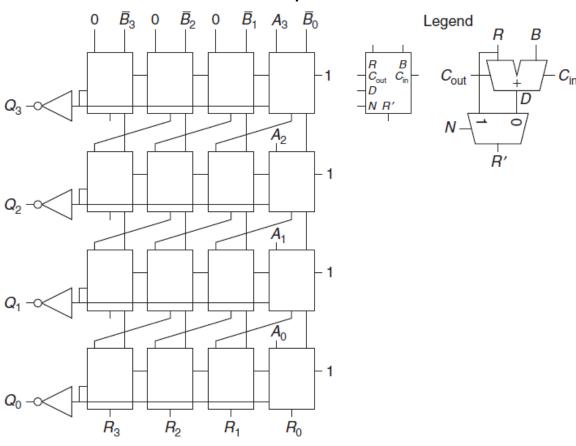

#### **Division**

Binary division can be performed using the following algorithm for N-bit unsigned numbers in the range  $[0, 2^{N}-1]$ :

```

\begin{array}{l} R' = 0 \\ \text{for } i = N-1 \text{ to } 0 \\ R = \left\{ R' \, << \, 1 \, , \, A_i \, \right\} \\ D = R - B \\ \text{if } D < 0 \text{ then } \quad Q_i = 0 \, , \, R' = R \quad // \, \, R < B \\ \text{else} \qquad \qquad Q_i = 1 \, , \, R' = D \quad // \, \, R \geq B \\ R = R' \end{array}

```

The partial remainder R is initialized to 0. The most significant bit of the dividend A then becomes the least significant bit of R. The divisor B is repeatedly subtracted from this partial remainder to determine whether it fits. If the difference D is negative (i.e., the sign bit of D is 1), then the quotient bit Qi is 0 and the difference is discarded. Otherwise, Qi is 1, and the partial remainder is updated to be the difference. In any event, the partial remainder is then doubled (left-shifted by one column), the next most significant bit of A becomes the least significant bit of R, and the process repeats. The result satisfies:

$$\frac{A}{B} = Q + \frac{R}{B}.$$

A schematic of a **4-bit Array Divider** is shown in the figure. The divider computes A/B and produces a quotient Q and a remainder R. The legend shows the symbol and schematic for each block in the array divider. The signal N indicates whether R - B is negative. It is obtained from the D output of the leftmost block in the row, which is the sign of the difference.

The delay of an N-bit array divider increases proportionally to  $N^2$  because the carry must ripple through all N stages in a row before the sign is determined and the multiplexer selects R or D. This repeats for all N rows. Division is a slow and expensive operation in hardware and therefore should be used as infrequently as possible.

#### **Four-bit Array Divider bit**

# tixed-Point Number System: -

A fixed-point notation has an implied binary point between the integer and fraction bits.

Example:1  $0110 \cdot 1100$ ,  $= 2 + 2 + 2 + 2 + 2 = 6.75_{10}$

Signed fixed-point numbers can use either signs magnitude notation or 2 scomplement notation.

$\frac{\text{Example: 2}}{+2.375} = 0010.0110$ -2.375 = 1010.0110 (Sign and magnitude) = 1101.1010 (2's complement)

Example: 3 Arithmetic Compute 0.75 + - 0.625 using fixed-point numbers

Compute U.15.

| 0.75 = 0000.1100] | Fixed-part numbers |

| +0.625 = 0000.10100 |

| +(-0.625) = 1111.01102(2's Complement) | applications that require |

| provision | Set not a 0.125 (00000.0010 => 0.125,0

large range

Floating-Point Number System: -

Floating-Point numbers have a sign; Mantissa (M), Base (B) and Exponent (E) as shown below. ±M x RE

For example, number 4.1×10 is the scientific notation for 4100. It has a M= 4·1, B=10, E= 3.

Floating-point numbers are base 2 with binary martissa. A 32-bit FPN hous 1 sign bit (MSb), 8 Exponent bits and . 23 Mantissa bits.

Example: - 32-bit Floating-Point Numbers

Regresset 22810 as a 32-bit FPN

==01:

== 1:11001 x 2 (Non

Signbit is 0 (Positive)

Exponent is 70 > 000001112 (8-bits).

Mantissa is remaining 23 bits 1110010....

In the binary FPN, the 1st bit of Mantissa is alway 1 and 50 need not be stored. It is called the implicit leading one:

In the modified FPN, this implicit leading one (hidden one) is not included in the 23-bit Mantissa for efficiency. Only the fraction bits are stored. This frees up extend bit for use fill deta.

Then one final modification is made to exponent field. The exponent need to represent both positive and negative exponents. To do so, use a Biased Exponent, got by adding a const bias of 127 to the original exponent.

So, exponent 7 becomes biased exponent 7+127=134=10000110,

if the exponent is -4, biased exponent is -4+127=123=011110112

#### Special Cases: $0, \pm \infty$ , and NaN

The IEEE floating-point standard has special cases to represent numbers such as zero, infinity, and illegal results. For example, representing the number zero is problematic in floating-point notation because of the implicit leading one. Special codes with exponents of all 0's or all 1's are reserved for these special cases. Table shows the floating-point representations of  $0, \pm \infty$ , and NaN. As with sign/magnitude numbers, floating- point has both positive and negative 0. NaN is used for numbers that don't exist, such as  $\sqrt{-1}$  or  $\log_2(-5)$ .

| Number | Sign | Exponent | Fraction                                |

|--------|------|----------|-----------------------------------------|

| 0      | X    | 00000000 | 000000000000000000000000000000000000000 |

| 00     | 0    | 11111111 | 000000000000000000000000000000000000000 |

| -∞     | 1    | 11111111 | 000000000000000000000000000000000000000 |

| NaN    | X    | 11111111 | Non-zero                                |

#### Single- and Double-Precision Formats

So far, we have examined 32-bit floating-point numbers. This format is also called single-precision, single, or float. The IEEE 754 standard also defines 64-bit double-precision numbers (also called doubles) that provide greater precision and greater range. Table shows the number of bits used for the fields in each format.

Excluding the special cases mentioned earlier, normal single-precision numbers span a range of  $\pm 1.175494 \times 10^{-38}$  to  $\pm 3.402824 \times 10^{38}$ .

They have a precision of about seven significant decimal digits (because  $2^{-24} \approx 10^{-7}$ ). Similarly, normal double-precision numbers span a range of  $\pm 2.22507385850720 \times 10^{-308}$  to  $\pm 1.79769313486232 \times 10^{308}$  and have a precision of about 15 significant decimal digits.

| Format | Total Bits | Sign Bits | Exponent Bits | Fraction Bits |

|--------|------------|-----------|---------------|---------------|

| single | 32         | 1         | 8             | 23            |

| double | 64         | 1         | 11            | 52            |

#### **Rounding**

Arithmetic results that fall outside of the available precision must round to a neighboring number. The rounding modes are: round down, round up, round toward zero, and round to nearest. The default rounding mode is round to nearest. In the round to nearest mode, if two numbers are equally near, the one with a 0 in the least significant position of the fraction is chosen.

Recall that a number overflows when its magnitude is too large to be represented. Likewise, a number underflows when it is too tiny to be represented. In round to nearest mode, overflows are rounded up to  $\pm \infty$  and underflows are rounded down to 0.

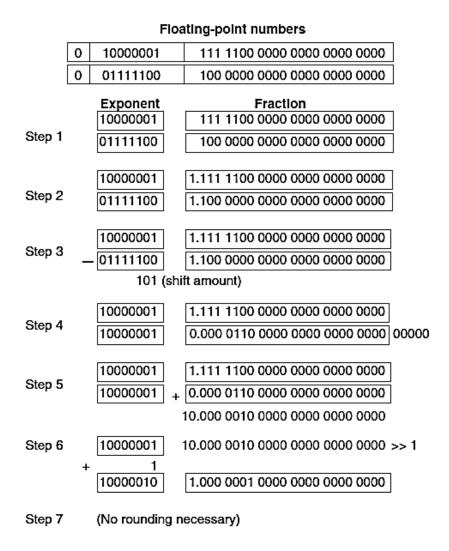

#### **Floating-Point Addition**

Addition with floating-point numbers is not as simple as addition with two's complement numbers. The steps for adding floating-point numbers with the same sign are as follows:

- 1. Extract exponent and fraction bits.

- 2. Prepend leading 1 to form the mantissa.

- 3. Compare exponents.

- 4. Shift smaller mantissa if necessary.

- 5. Add mantissas.

- 6. Normalize mantissa and adjust exponent if necessary.

- 7. Round result.

- 8. Assemble exponent and fraction back into floating-point number.

Example shows the floating-point addition of 7.875 (1.11111  $\times$  2<sup>2</sup>) and 0.1875 (1.1  $\times$  2<sup>-3</sup>).

The result is  $8.0625 (1.0000001 \times 23)$ .

After the fraction and exponent bits are extracted and the implicit leading 1 is prepended in steps 1 and 2, the exponents are compared by subtracting the smaller exponent from the larger exponent. The result is the number of bits by which the smaller number is shifted to the right to align the implied binary point (i.e., to make the exponents equal) in step 4. The aligned numbers are added. Because the sum has a mantissa that is greater than or equal to 2.0, the result is normalized by shifting it to the right one bit and incrementing the exponent. In this example, the result is exact, so no rounding is necessary. The result is stored in floating-point notation by removing the implicit leading one of the mantissa and prepending the sign bit.

#### Some interesting facts...

Floating-point cannot represent some numbers exactly, like 1.7. However, when you type 1.7 into your calculator, you see exactly 1.7, not 1.69999. . . . To handle this, some applications, such as calculators and financial software, use binary coded decimal (BCD) numbers or formats with a base 10 exponent. BCD numbers encode each decimal digit using four bits with a range of 0 to 9. For example, the BCD fixed-point notation of 1.7 with four integer bits and four fraction bits would be 0001.0111. Of course, nothing is free. The cost is increased complexity in arithmetic hardware and wasted encodings (A–F encodings are not used), and thus decreased performance. So for computer-intensive applications, floating-point is much faster.

Floating-point arithmetic is usually done in hardware to make it fast. This hardware, called the floating-point unit (FPU), is typically distinct from the central processing unit (CPU). The infamous floating-point division (FDIV) bug in the Pentium FPU cost Intel \$475 million to recall and replace defective chips. The bug occurred simply because a lookup table was not loaded correctly!

# Architecture:

1

The architecture of the Computer is represented by the Instruction Set and Operand locations within Registers and Memory. It is the programmer's view of the Computer.

Many different Architectures exist, such as IA-32, MIPS, SPARC and PowerPC. The complete vocabilary of the Instructions of a Computer is its Instruction Set. Computer instructions include add, subtract, and jump and so on.

They indicate both the operation to perform and the Operands to use. The Operands may come from Memory, from Registers or from the Instruction itself, as indicated by the Addressing mode used. Every Architecture has its own language which is internally in bitrary format. So Intructions are in the form of bits.

However, for the ease of use by Programmer (Humans), a symbolic language format is used to represent instructions and the program that is called Assembly language.

Assembly language is the human-readable representation of the computer's native language. Each assembly language instruction specifies both the operation to perform and the Operands on which to operate.

MIPS Architecture instructions are considered for Assembly language statements using registers, memory and constants.

Assembly language instructions form a program, that is converted to machine language of native architecture using Assembler. Hence Assembly language is machine (architecture) dependent: On the other hand, High Level Languages such as C, C++, Java are machine independent and use Interpreters or Compilers.

Patterson and Hennessy Principles Dosign Principle 1: Simplicity favours Regularity. The add and sub have consistent introduce format and also a consistent number of operands, the sources and one destruction. Those are seasier to encode and handle in hardware. Deris Principle 2: - Make the Common Case fast Use of multiple assembly language instactions to perform more complex operations. Deriga Principle 3: Smaller is faster. The fewer the registers, the faster they can be accessed. Dezign Principle 4: - Good design demands good Compromiss A Single instruction format would be simple but not flexible. The MIPS in his set makes the compromise of sporting these instruction formats. A computer architecture does not define the underlying hardware implementation. So, many different how implementations of a single For example, Intelland Advanced Micro Devices (AMD), both sell various microprocessors belonging to the same X86 architecture. They all our the same programs; Let be different underlying how and so offen trade-offs, a Performance, like and Power. Some microproletion are optimized for high performance servers , where others are optimized for long battery life in laptops. MIPS Architecture - Leveliped by John Hennessey at Stanford in 1980s It is vied in Silicon Graphics, Nintendo and CISCO.

# Instructions:

The most common operation computes perform is Addition.

Example: -1

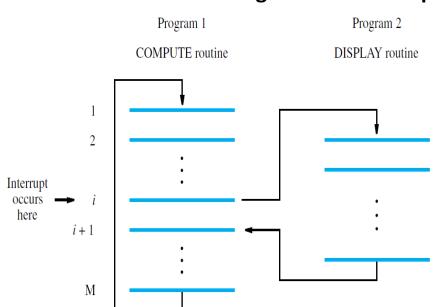

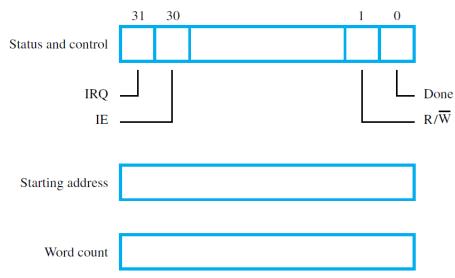

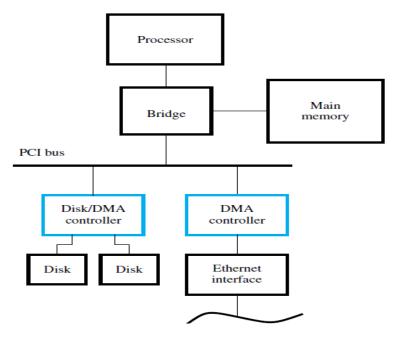

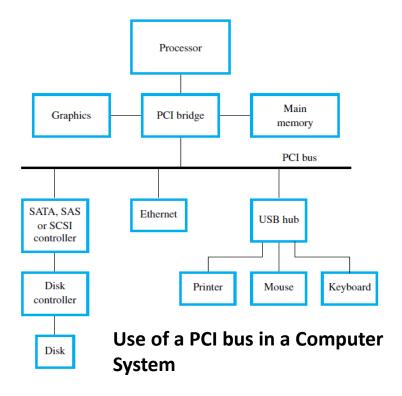

Write code for adding variables b and c and writing result to a, in both high level language i.e., C and in MIPS assembly language.